引言

床旁磁共振成像(Point-on-Care MRI,POC MRI)是一种创新性的、可在床边进行MRI的技术,具有周转时间短、临床成像图像质量高等优点[13

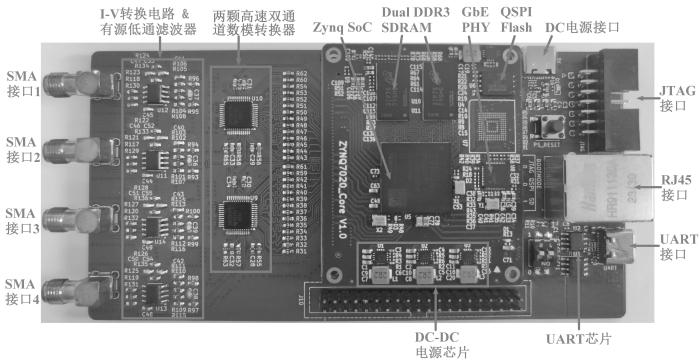

基于此,本文提出了一种基于Zynq 7000 SoC全可编程片上系统的便携式磁共振多源射频脉冲发生器的设计方案. 硬件设计平台采用Xilinx公司的第一代全可编程片上系统,芯片型号为XC7Z020-2CLG400I. 该芯片在处理器系统(Processor System,PS)端集成高性能RISC微处理器(Advanced RISC Machines,ARM)和在可编程逻辑(Programmable Logic,PL)端集成可编程逻辑门资源丰富的FPGA,同时还集成PLL、DSP、嵌入式块随机存取存储器(Block Random Access Memory,BRAM)等其他硬件资源. 芯片内部采用统一的AXI4(Advanced eXtensible Interface,AXI)总线协议和AXI4接口进行高速互联通信,并且支持用户使用硬件描述语言编写带AXI4接口的自定义IP核,因此十分适用于高带宽、可重构性强的多源射频脉冲发生器设计. 同时充分利用全可编程SoC的高集成度优势,利用ARM处理器实现对存储的射频脉冲参数和波形文件数据进行预处理和与上位机的千兆以太网通信,利用FPGA实现对AXI DDS自定义IP核的配置和高精度并行发射多路射频脉冲信号. 因此,本文自制的射频硬件电路板尺寸仅有14 cm×7 cm,约两张信用卡大小,非常小巧紧凑. 与使用文本格式的高级编程语言(如C++,PASCAL)编写的上位机软件不同的是,实验室虚拟仪器工程平台(Laboratory Virtual Instrument Engineering Workbench,LabView)是由美国国家仪器公司研发的图形化程序开发环境,降低了软件编程门槛,缩短了软件开发周期,因此个人计算机(Personal Computer,PC)端上位机软件采用LabView编程,实现用户配置射频脉冲参数、波形类型和与射频硬件电路单元的千兆以太网通信,以及磁共振信号的存储和显示的功能.

1 系统结构

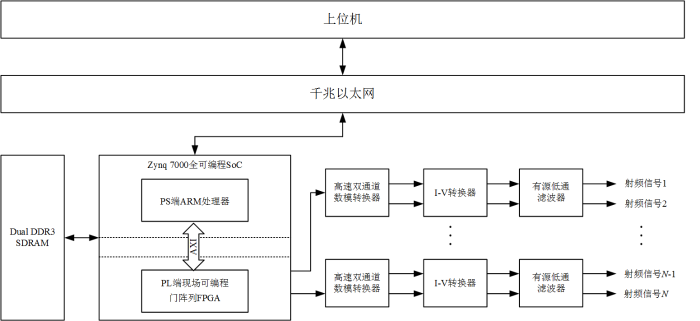

本文提出的多源射频脉冲发生器设计方案主要分为三个单元,包括射频硬件电路单元、Zynq 7000全可编程SoC单元和PC端上位机单元,系统结构框图如图1所示. 在这项工作中,Xilinx的XC7Z020-2CLG400I芯片负责整个射频硬件电路单元的逻辑控制和数据处理. 它通过千兆以太网RJ45接口接收来自上位机的射频脉冲参数和波形类型数据,捕获的数据存储在具有32位数据总线宽度的PS端1 GB双通道双倍数据速率同步动态随机存储器(Dual Double-data-rate 3 Synchronous Dynamic RAM,Dual DDR3 SDRAM)中. 为了提高射频脉冲参数和波形文件数据的传输速度,PS端ARM处理器控制S_AXI_HP0接口,从Dual DDR3 SDRAM中直接读取数据并将其传输到PL端的FPGA. 在这里,数据由具备并行处理能力和流水线执行功能的高速数字单元进行处理. FPGA部分主要侧重于射频脉冲信号生成和调制,采用的设计包含Xilinx IP核和本文编写的自定义IP核,其中利用硬件描述语言开发的AXI DDS自定义IP核是本系统的核心,它将来自PS端的射频脉冲参数和波形文件数据生成特定的调制信号和载波信号. 接着将不同的调制信号和载波信号调制成特定的数字射频脉冲信号输出给具有双通道、275 MSPS更新速率、 14 bit高分辨率、14位并行输入端口、最大20 mA互补电流输出的高速数模转换器(Digital to Analog Converter,DAC)芯片(DAC5672A),经由运算放大器构建的跨阻放大器(I-V转换器)和有源低通滤波器处理得到电压输出范围为-864 mV~+864 mV的模拟射频脉冲信号.

图1

图1

多源射频脉冲发生器系统框图

Fig. 1

Block diagram of multi-source RF pulse generator system

1.1 射频硬件电路单元

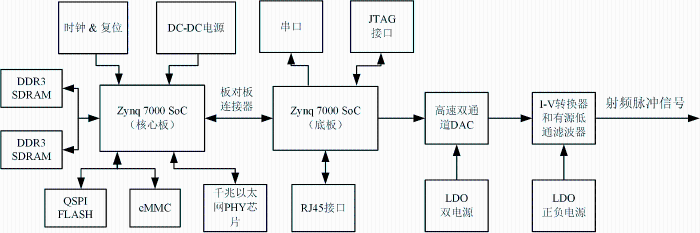

为了实现高性能、便携式磁共振多源射频脉冲发生器的设计要求,使用更为先进的芯片进一步提升集成度,使得数字化射频硬件电路单元更加小型化. 利用Altium Design软件(版本号21.9.1)自主设计了多源射频脉冲发生器硬件电路单元,结构框图如图2所示,采用“核心板 + 底板”的模块化结构,使得硬件电路单元设计更加灵活通用. 首先根据已经确定的系统功能和技术指标划分为若干个电路功能模块,包括电源管理模块、Zynq 7000 SoC最小系统模块、千兆以太网模块、高速DAC模块、I-V转换器模块、有源低通滤波器模块等. 其次绘制元件符号库和元件封装库,按照划分好的电路功能模块依次绘制对应的电路原理图,进行电气规则检查,保证原理图电路连接的合理性和正确性,在完成上述工作后将原理图网表文件导入印刷电路板设计(Printed Circuit Board Layout,PCB Layout)界面进行布局布线. 为了满足信号完整性的要求,采用8层高速PCB设计,叠层顺序为:信号层1-地层-信号层2-地层-电源层-信号层3-地层-信号层4. 鉴于DDR3 SDRAM需要进行高速、高带宽数据读写要求,所以布局布线采用Fly-By拓扑结构. 整板单端布线阻抗控制在50 Ω,差分对布线阻抗控制在100 Ω. 此外,差分对内部误差范围控制在±5 mil(1 mil ≈ 0.025 4 mm)以内,数据总线误差范围控制在±10 mil以内,地址总线、控制总线和时钟线的误差范围控制在±25 mil以内.

图2

1.2 Zynq 7000全可编程SoC单元

1.2.1 可编程逻辑硬件设计

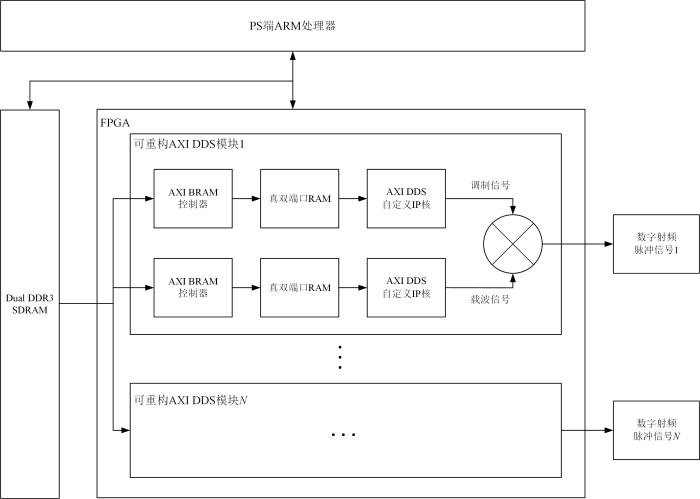

在本设计中,可编程逻辑硬件设计是多源射频脉冲发生器的核心,由PLL、AXI BRAM控制器、真双端口RAM、乘法器、AXI DDS自定义IP核等部分构成,实现多路信号的可重构直接数字频率合成和射频脉冲信号调制等功能,极大地赋予了硬件灵活性. 可编程逻辑硬件设计分为两个子部分:载波信号和调制信号生成部分以及射频脉冲信号调制部分.(1)载波信号和调制信号生成部分:单个可重构的AXI DDS模块结构如图3所示. 在PLL倍频后的400 MHz时钟信号和AXI BRAM控制器的作用下,接收来自PS端处理后的射频脉冲参数和波形文件数据,存储在由Block Memory Generator构建的真双端口RAM中,接着读取真双端口RAM中的波形数据到AXI DDS自定义IP核中,实现调制信号和载波信号的数字波形输出. (2)射频脉冲信号调制部分:在400 MHz时钟信号作用下,多个可重构AXI DDS模块生成的多路特定的调制信号和载波信号,经乘法器将调制信号和载波信号进行调制,得到多路特定的数字射频脉冲信号. 在Vivado软件中多次例化可重构AXI DDS模块,就可以产生和调制出多个数字射频脉冲信号,极大地发挥FPGA的硬件可重构性,满足多源射频脉冲发生器的多通道并行发射技术要求.

图3

图3

可重构AXI DDS模块结构示意图

Fig. 3

Schematic diagram of the reconfigurable AXI DDS module structure

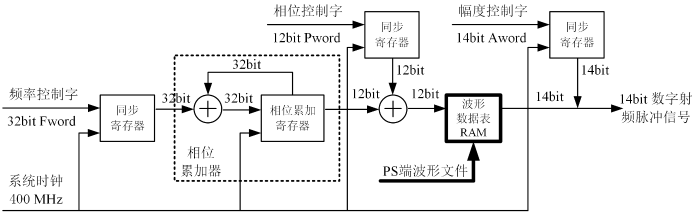

在可编程逻辑设计中,可重构AXI DDS模块是其核心. AXI4总线协议和AXI4接口的应用是Xilinx Zynq 7000系列SoC芯片最成功的举措,它将擅长逻辑控制的ARM处理器与擅长并行计算的FPGA紧密地结合在一起,并且支持用户使用硬件描述语言编写带AXI4接口的自定义IP核. 本文依据DDS原理,使用Verilog语言编写FPGA代码,并进行代码仿真、RTL分析、综合、得到一个性能与Xilinx DDS IP核相似的AXI DDS自定义IP核,如图4所示. 该IP核频率控制字位宽为32 bit,当系统时钟为400 MHz时,频率精度约为0.093 Hz. 相位控制字位宽为12 bit,相位精度约为0.088˚,波形数据表RAM存储一个完整周期的波形,存储深度为4 k,采样值位宽为14 bit. DDS工作过程是:一个时钟周期内,32 bit频率控制字和相位累加器相加一次,得到一个32 bit位宽的累加值,取其高12位作为相位增量与12 bit相位控制字相加后得到一个12 bit二进制数值作为波形数据表RAM的地址去查表得到波形数据采样值,完成相位到幅度的转变. 最后由幅度控制字对波形幅度进行调节,得到一个14 bit数字射频脉冲信号. 该IP核作为子模块,AXI4协议及其接口作为其上层模块,一同封装成一个带AXI4接口的AXI DDS自定义IP核,其优势是在PC端上位机图形用户界面选择波形类型,PS端就会加载不同的波形文件,传输到PL端生成特定的数字射频脉冲波形信号,灵活性优于仅能生成正弦波和余弦波的Xilinx DDS IP核.

图4

1.2.2 应用处理器软件设计

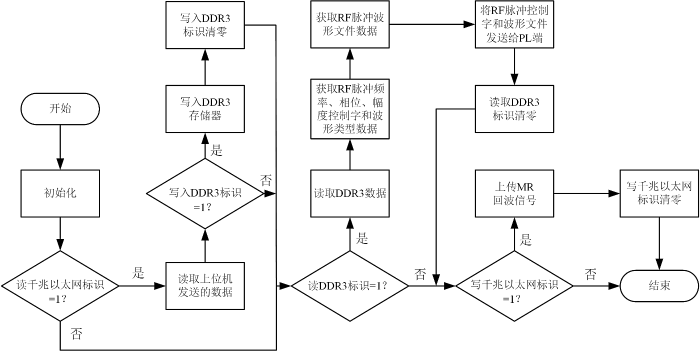

自制的射频硬件电路单元采用XC7Z020-2CLG400I全可编程SoC芯片作为主控制芯片,该芯片片内集成双核ARM Cortex-A9高速处理器硬核,运行时钟频率高达766 MHz,逻辑运算能力完全满足本设计的技术需求. 在本设计中,应用处理器软件设计主要实现的功能是与PC端的上位机建立千兆以太网通信,并且对射频脉冲信号的频率控制字、相位控制字、幅度控制字和射频脉冲波形文件进行数据处理,并且将这些处理过的数据发送给可编程逻辑. 应用处理器软件设计流程图如图5所示.

图5

应用处理器软件设计工作流程如下:程序开始,对通用输入输出GPIO、中断、千兆以太网、AXI DDS等外设进行初始化,初始化完成后进入中断等待状态. ARM处理器通过三个中断控制器来完成所有工作:1号中断是用来通知ARM处理器处理来自上位机的千兆以太网连接请求并进行连接. 当读千兆以太网标识位置位后,读取上位机发送下来的射频脉冲控制字和波形类型数据,并置位写入DDR3标识位,置位后将数据写入Dual DDR3 SDRAM暂存起来并清零标识位. 2号中断是用来响应FPGA的中断请求,读取Dual DDR3 SDRAM存储器暂存的射频脉冲控制字和波形文件数据,一并发送给FPGA并清零标识位. 3号中断是响应MR回波上传至上位机的中断请求. 当MR回波信号数据传输到Dual DDR3 SDRAM时,置位写千兆以太网标识位,ARM处理器启动千兆以太网控制器外设,将MR回波数据上传至PC端上位机并清零标识位.

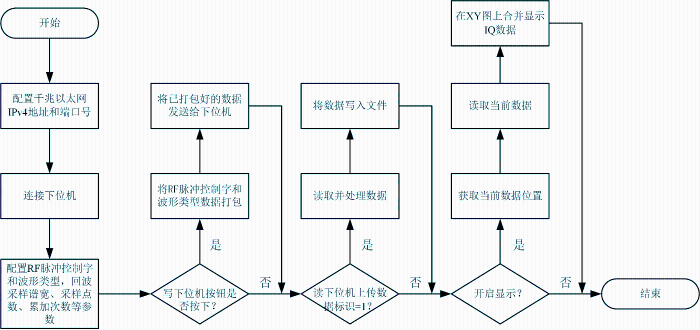

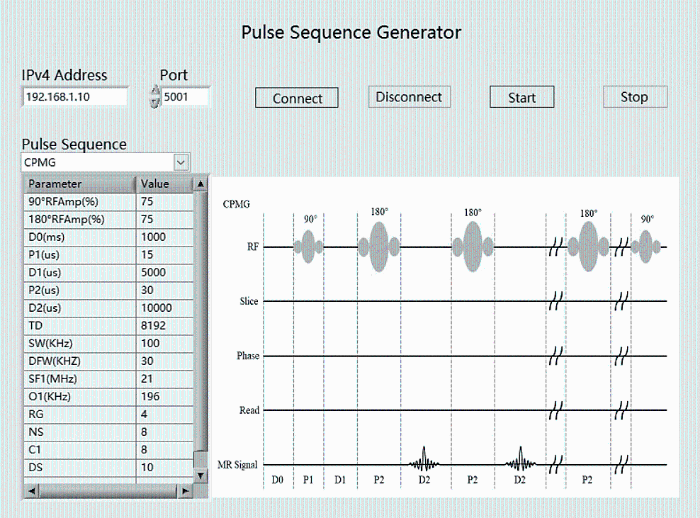

1.3 PC端上位机单元设计

LabView采用图形化G语言编程,以数据流驱动方式运行. 在本设计中,PC端上位机程序首先通过输入控件配置IPv4地址和端口号,与下位机射频硬件电路单元建立千兆以太网通信连接,实现两个组件之间1 000 Mb/s的数据读写速度. 上位机的列表控件包括射频脉冲频率、相位、幅度及作用时间和MR回波信号的采样谱宽、采样点数、累加次数等参数,用户可通过列表输入控件修改这些参数以实现最佳的接收效果. 同时上位机还显示特定脉冲序列示意图,优化用户设置MRI参数操作. 通过触发写下位机布尔按钮写入下位机的操作,将这些特定参数打包并传送到射频硬件电路单元. 当上位机接收到射频硬件电路单元上传的MR回波数据后,会将接收到的十六进制数据转换为I和Q两路有符号十进制数,然后根据预定的读取点数将数据写入文件存储,并使用XY图形控件显示IQ数据. 上位机的软件设计流程图如图6所示.

图6

2 结果与讨论

2.1 硬件电路单元实验

本文提出的便携式磁共振多源射频脉冲发生器是在自制的数字化射频硬件电路单元上实现的,如图7所示. 电路板的尺寸为14 cm×7 cm,大致相当于两张信用卡大小. 为了验证所设计的硬件电路正确性,利用Xilinx FPGA集成开发环境(Integrated Development Environment,IDE)在电路板上进行了两项测试. 首先,为了评估射频硬件电路板的鲁棒性,对板载1 GB Dual DDR3 SDRAM进行连续写入压力测试. 测试Demo程序由Vivado 2020.2和Vitis 2020.2提供,配置的SDRAM时钟频率(双倍数据速率)为1 066 MHz,设置SDRAM测试长度为1 023 MB,设置数据总线位宽为32 bit,整个内存测试由15个子测试组成,每个子测试使用不同的数据模式,表1显示了其测试结果. 所有子测试分成四种类型:递增模式 (Memtest_0)、写入一个指定的32 bit数据模式 (Memtest_s)、干扰模式 (Memtest_p)和伪随机模式 (Memtest_l). 以上所有子测试的工作流程都是首先按顺序将每个子测试生成的数据写入整个DDR3存储空间,然后读取出来并与写入值进行比较,统计出现错误的个数. 测试结果表明,所有子测试的字和字节读取值与写入值的比较出现错误计数均为0且同一类型的数据模式耗时相似. 因此XC7Z020芯片和1 GB Dual DDR3 SDRAM之间的数据传输无误码,并且带宽达到了4.264 GB/s. 对于四种类型数据模式所用时间不同的原因分析,Memtest_0、Memtest_p和Memtest_l这三类数据模式需要ARM处理器进行较复杂的逻辑控制和数据处理才能生成测试所用的数据,然后写入DDR3存储器中,因此耗时较长. 而Memtest_s数据模式是ARM处理器直接将指定的32 bit数据写入DDR3存储器中,因此耗时最短.

图7

表1 1 GB Dual DDR3 SDRAM的15个内存子测试数据模式及连续写入压力测试结果

Table 1

| 子测试 | 数据模式描述 | 比较字和字节读取值 与写入值出现错误计数 | 耗时/s |

|---|---|---|---|

| Memtest_0 (0) | 递增模式, 写入每个内存地址的唯一值(数据 = 地址) | 0 | 35.6024 |

| Memtest_s (1) | 写入0x00000000 | 0 | 22.9253 |

| Memtest_s (2) | 写入0xFFFFFFFF | 0 | 22.9270 |

| Memtest_s (3) | 写入0xAAAAAAAA | 0 | 22.9270 |

| Memtest_s (4) | 写入0x55555555 | 0 | 22.9253 |

| Memtest_s (5) | 交替写入0x00000000和0xFFFFFFFF | 0 | 22.9270 |

| Memtest_s (6) | 交替写入0xFFFFFFFF和0x00000000 | 0 | 22.9270 |

| Memtest_s (7) | 交替写入0x55555555和0xAAAAAAAA | 0 | 22.9270 |

| Memtest_s (8) | 交替写入0xAAAAAAAA和0x55555555 | 0 | 22.9253 |

| Memtest_p (9) | 干扰模式: 8 bits中每bit相同且每bit干扰一次 | 0 | 35.0279 |

| Memtest_p (10) | 干扰模式: 8 bits中每bit反转且每bit干扰一次 | 0 | 35.0385 |

| Memtest_l (11) | 具有不同种子的伪随机模式 | 0 | 36.6623 |

| Memtest_l (12) | 具有不同种子的伪随机模式 | 0 | 36.6623 |

| Memtest_l (13) | 具有不同种子的伪随机模式 | 0 | 36.6623 |

| Memtest_l (14) | 具有不同种子的伪随机模式 | 0 | 36.6623 |

为了建立上位机与射频硬件电路单元之间的高速通信方式,本文设计了一个千兆以太网模块,并对其性能进行了测试. 测试Demo程序由Vivado 2020.2和Vitis 2020.2提供,在具有以下规格的计算机上执行:Intel Core i7-12700H CPU,运行Windows10 21H1操作系统,配备16 GB运行内存和1 TB SSD固态硬盘. 所用的网络性能测试工具为iperf3,打开Windows cmd.exe命令行程序界面,输入“iperf -c 192.168.1.10 -i 5 -t 30 -w 2M”命令,启动iperf3软件,工作模式为客户端模式,连接到服务器IPv4地址为192.168.1.10,指定TCP窗口大小为2 MB,测试总时长为30 s,每隔5 s打印一次输出信息. 测试结果如表2所示,在30 s测试时间内,总计连续传输3 111 MB数据,平均带宽为870 Mb/s. 这些结果表明,射频硬件电路单元和PC端上位机之间的千兆以太网通讯链路正常并且达到了预期的传输速率. 对于千兆以太网的理论传输速率来说,这次测试的平均带宽是一个合理值,分析原因可能是核心板与底板之间的板对板连接器不满足 1 000 Mb/s的传输等级和传输链路受到周边负载设备的噪声干扰导致的.

表2 千兆以太网传输速率测试结果

Table 2

| 时间间隔/s | 传输数据量/(MB) | 带宽/(Mb/s) |

|---|---|---|

| 0.0~5.0 | 540 | 905 |

| 5.0~10.0 | 518 | 869 |

| 10.0~15.0 | 512 | 860 |

| 15.0~20.0 | 519 | 871 |

| 20.0~25.0 | 516 | 866 |

| 25.0~30.0 | 506 | 849 |

| 0.0~30.0 | 3111 | 870 |

2.2 可编程逻辑硬件电路实验

对运行在Zynq 7000 SoC上的多源射频脉冲发生器原理进行分析,设计相应的可编程逻辑硬件电路并封装成AXI DDS模块的形式. 在Vivado软件中多次例化该模块以实现多通道数字射频脉冲信号的并行生成和调制,极大地发挥FPGA的硬件可重构性,同时在ARM处理器端编写软件程序以实现独立调节射频脉冲信号的频率、相位、幅度和波形类型,满足射频脉冲信号参数独立可调节且多通道并行发射的技术要求. 本文搭建了4通道射频脉冲发生器的FPGA硬件电路,且消耗的FPGA硬件资源较少,从表3可以看出,4通道射频脉冲发生器硬件电路消耗查找表(Look Up-Table,LUT)资源数量为4 872,占LUT资源总数的9.16%,消耗触发器(Flip-Flop,FF)资源数量为6 370,占FF资源总数的5.99%,消耗BRAM资源数量为13.5,占BRAM资源总数的9.64%,消耗输入输出(Input-Output,IO)资源数量为66,占IO资源总数的52.8%等. 4通道射频脉冲发生器功耗也较低,动态功耗1.786 W,静态功耗0.147 W,总功耗为1.933 W. 因为使用了两颗双通道14位并行输入端口的高速DAC芯片,所以FPGA的IO资源消耗较大. 对于16通道或更多通道数的多源射频脉冲发生器来说,可以选择Zynq 7000 SoC系列更多pin脚封装的SoC芯片.

表3 4通道射频脉冲发生器FPGA硬件资源消耗情况

Table 3

| 资源 | 消耗资源数量 | 可用资源总数 | 使用率/% |

|---|---|---|---|

| LUT | 4872 | 53200 | 9.16 |

| LUTRAM | 382 | 17400 | 2.20 |

| FF | 6370 | 106400 | 5.99 |

| BRAM | 13.5 | 140 | 9.64 |

| IO | 66 | 125 | 52.8 |

| BUFG | 1 | 32 | 3.13 |

2.3 射频脉冲波形发射实验

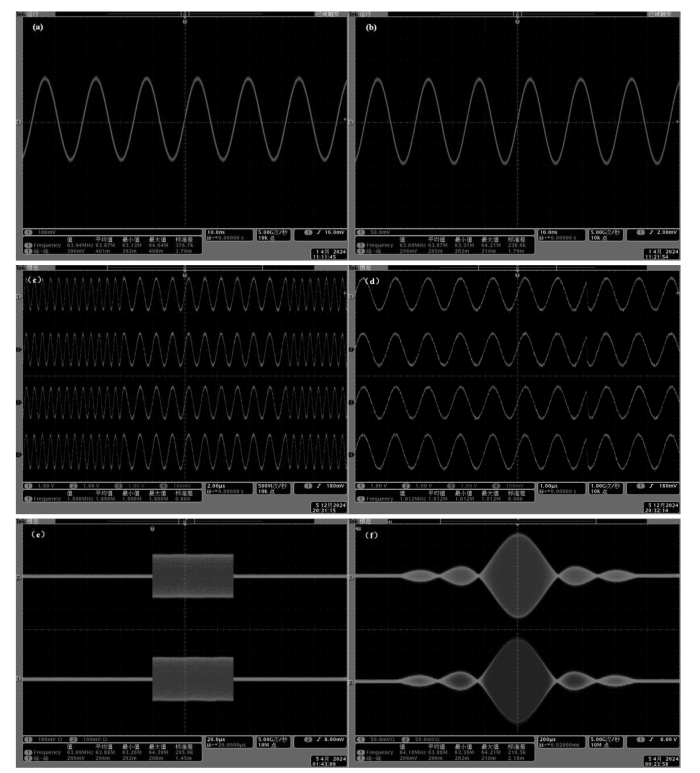

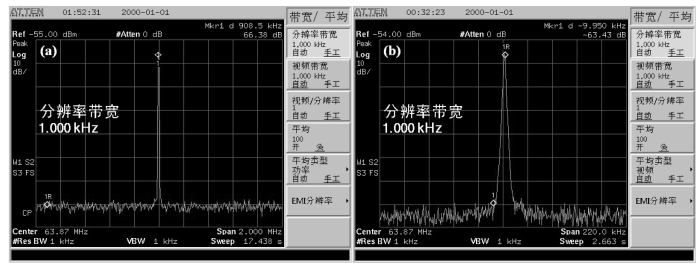

为了验证多源射频脉冲发生器射频脉冲波形发射效果,本文使用泰克MSO4104示波器对射频硬件电路单元4通道发射的射频硬脉冲和软脉冲波形进行测试. 在上位机和射频硬件电路单元连接好千兆以太网后,通过图形用户界面的输入控件设置射频脉冲信号参数,将这些参数打包并发送给射频硬件电路单元. 示波器采样到的射频脉冲波形如图8所示. 图8(a)是频率为63.87 MHz,峰峰值为401 mV的射频脉冲信号. 通过修改幅度控制字将峰峰值从401 mV快速调制到205 mV. 图8(b)是频率为63.87 MHz,峰峰值为205 mV的射频脉冲信号. 图8(c)是4通道快速频率调制结果图,通过修改频率控制字将频率从1 MHz快速调制到2 MHz,图8(d)是4通道快速相位调制结果图,通过修改相位控制字将相位从0快速调制到π. 从4通道同时输出波形来看,多通道同时激发功能正常且多通道之间的延迟和波形一致性都较好. 图8(e)是频率为63.88 MHz,峰峰值为206 mV的双通道射频硬脉冲波形信号. 图8(f)是频率为63.88 MHz,峰峰值为206 mV的双通道5-Sinc型射频软脉冲波形信号,输出负载阻抗均为50 Ω. 通道三和通道四输出效果同上. 采用ATTEN公司的AT6030D频谱分析仪对输出频率为63.87 MHz的射频脉冲信号进行频谱分析,分析结果如图9所示. 图9(a)是分辨率带宽为1 kHz,偏离中心频率10 kHz范围内的相位噪声约-64.57 dBc/Hz,图9(b)是分辨率带宽为1 kHz,偏离中心频率1 MHz范围内的杂散约为-67.23 dBc.

图8

图8

(a)频率为63.87 MHz,峰峰值为401 mV的射频脉冲信号;(b)频率为63.87 MHz,峰峰值为205 mV的射频脉冲信号;(c) 4通道快速频率调制,从1 MHz快速调制到2 MHz;(d) 4通道快速相位调制,从相位0快速调制到相位π;(e)频率为63.88 MHz,峰峰值为206 mV的双通道射频硬脉冲波形;(f)频率为63.88 MHz,峰峰值为206 mV的双通道5-Sinc射频软脉冲波形

Fig. 8

(a) RF pulse waveform at 63.87 MHz with 401 mV peak-to-peak; (b) RF pulse waveform at 63.87 MHz with 205 mV peak-to-peak; (c) 4-channel fast frequency modulation from 1 MHz to 2 MHz; (d) 4-channel fast phase modulation from phase 0 to phase π; (e) Dual-channel RF hard pulse waveform at 63.88 MHz with 206 mV peak-to-peak; (f) Dual-channel 5-Sinc RF soft pulse at 63.88 MHz with 206 mV peak-to-peak waveforms

图9

图9

(a)输出频率为63.87 MHz、频谱窗宽为2 MHz的射频信号频谱图;(b)输出频率为63.87 MHz、频谱窗宽为220 kHz的射频信号频谱图

Fig. 9

(a) Spectrogram of an RF signal with an output frequency of 63.87 MHz and a spectral window of 2 MHz; (b) Spectrogram of an RF signal with an output frequency of 63.87 MHz and a spectral window of 220 kHz

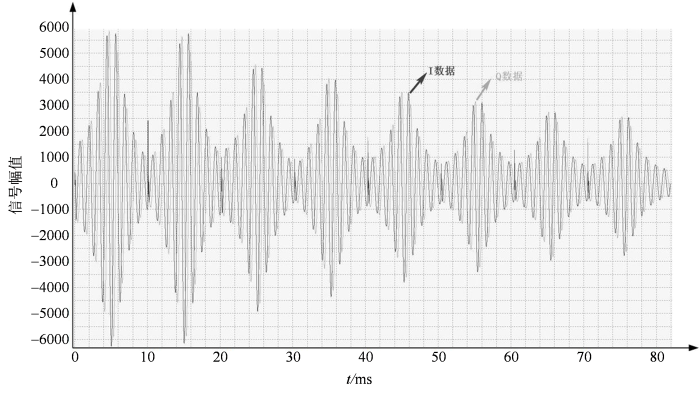

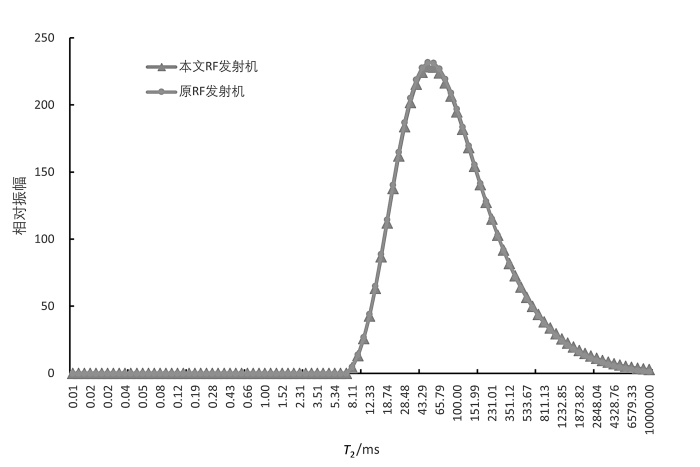

2.4 MR回波信号实验

为了验证本文设计的多源射频脉冲发生器发射效果,用本发射机替换实验室自制的0.5 T MRI原发射机,并且用本文设计的上位机软件配置脉冲序列参数和显示接收到的磁共振回波信号. MRI系统的永磁体由钕铁硼材料制成,呈H型结构,0.5 T磁场强度,磁极直径165 mm,磁极间隙35 mm,磁场均匀度2.5 ppm (1 ppm=10-6),温度系数约为±20 ppm. 射频功率放大器采用AB类工作模式,以获得良好的线性度的同时提高功率放大效率,降低发热,输入阻抗和输出阻抗均为50 Ω,输出功率为100 W. 本实验选用大豆油作为实验样品,用硬脉冲CPMG序列进行实验. 硬脉冲CPMG序列是在自旋回波序列基础上,多次施加180˚射频脉冲,从而得到多个回波信号的回波脉冲序列. 本文在进行硬脉冲CPMG序列时设置参数如下,如图10所示:90˚脉冲施加时间P1为15 μs,180˚脉冲施加时间P2为30 μs,脉冲施加强度均为75%;脉冲序列重复时间D0为1 000 ms,90˚脉冲与180˚脉冲之间的时间间隔D1为5 ms;采样点数TD为8 192,采样频率SW为100 kHz,即采样时间为81.92 ms;回波时间TE为10 ms,回波信号个数C1为8,累加次数NS为8. 上位机接收信号进行8次累加后结果如图11所示,其中横坐标为时间,每一格代表2 ms,纵坐标为量化后的信号幅值. 由上位机显示的硬脉冲CPMG序列的磁共振回波信号可以看出,在施加一个90˚脉冲后,连续对样品施加8次180˚脉冲,得到8个回波信号,并且回波信号的幅度逐渐减小. 采集到MR回波信号后,利用最小二乘法做弛豫时间反演,求得横向弛豫时间T2反演结果. 本文发射机和原发射机得到的MR回波实际数据反演结果比较如图12所示. 从图中可以看出,两者反演得到的T2谱形态高度相似,主要分布区间基本一致,谱峰位置与幅度吻合良好. 表明本文设计的发射机在激励产生有效回波信号方面达到了预期效果,其采集到的信号质量与原发射机相当,能够可靠地用于T2弛豫时间反演,获得符合实际的结果. 该比较结果验证了本文发射机在实际应用中的有效性和可靠性.

图10

图11

图11

硬脉冲CPMG序列的MR回波信号图

Fig. 11

MR echo signal map of a hard-pulsed CPMG sequence

图12

3 结论与展望

本文提出了一种基于Zynq 7000 SoC和LabView的便携式磁共振多源射频脉冲发生器设计,它通过多源射频发射技术和更高集成度的硬件电路设计来提高磁共振设备的信噪比和小型化. 在应用处理器端加载特定的波形文件和在可编程逻辑端多次例化AXI DDS模块来产生和调制出多路特定的射频脉冲信号,充分发挥FPGA的硬件可重构性. 硬脉冲CPMG序列磁共振回波信号实验是在一块自制的射频硬件电路单元上实现发射的,它仅有约两张信用卡大小. 此外,还利用LabView图形编程平台开发了PC端具备图形用户界面的上位机软件,可全面访问并修改脉冲序列参数和显示脉冲序列示意图,优化参数设置流程的同时便于用户操作. 实验结果证明,本文设计的磁共振多源射频脉冲发生器可以正确发射上位机配置参数的射频脉冲波形. 此外,它还提高了硬件电路系统的集成度,降低了功耗,硬件可重构性方面优于前人研究的射频脉冲发生器. 在未来的工作中,利用更大FPGA资源的Zynq 7000 SoC系列芯片,将梯度脉冲发生器、射频脉冲接收器和脉冲序列发生器集成在同一片SoC上,将进一步实现谱仪的小型化,拓宽便携式磁共振设备的应用领域.

利益冲突

无

参考文献

Magnetic resonance imaging RF pulse generator based on FPGA and DDS

[J].

基于FPGA与DDS的磁共振成像射频脉冲发生器

[J].

DOI:10.11938/cjmr20160408

[本文引用: 1]

设计了一种基于现场可编程门阵列(FPGA)与直接数字频率合成(DDS)的磁共振成像(MRI)射频脉冲发生器,采用FPGA实现DDS,并内置软脉冲波形双端口随机存取存储器(RAM)、乘法器以及相关的控制逻辑.实现了较高的技术指标,其中频率、相位与幅度分辨率分别为32 bits、16 bits与16 bits,软脉冲波形的时间精度可达0.1 μs.FPGA提供了一个可编程的接口,便于序列控制器对其进行控制,以输出射频脉冲.MRI实验结果证明了该设计的可行性.

Nuclear magnetic resonance RF pulse generator based on digital modulation technique

[J].

基于数字调制技术的核磁共振射频脉冲发生器

[J].在核磁共振(NMR)领域,射频脉冲信号的质量、形状对NMR性能及应用有着重要影响.本文基于现场可编程门阵列(FPGA)和直接数字频率合成(DDS)芯片AD9910设计了一种硬件结构更为简单的NMR射频脉冲发生器,实现了射频脉冲各项参数的数字化调制.其频率、相位、振幅的控制精度分别达到了32位、16位和14位,脉冲调制的时间精度为0.01 μs,可灵活生成持续时间不小于0.1 μs、载波频率不高于400 MHz的各类软脉冲和硬脉冲.同时,针对脉冲序列的特点建立了"脉冲+延时"的基础模型,提出了一种通用性更强的列表式脉冲序列控制方案,精简了对上级控制单元的控制需求.此外,对射频脉冲信号的频谱特性进行了理论分析,并采用Hanning窗对软脉冲的包络波形进行了优化处理,仿真和实验结果表明,Hanning窗可以有效抑制软脉冲的频谱泄漏问题.

Optimized design of selective RF pulses for simultaneous multilayer MRI

[J].

用于同时多层MRI的选择性射频脉冲的优化设计

[J].近年来,为提高磁共振成像(MRI)信号信噪比(SNR)、缩短成像时间,同时多层成像技术受到了极大的关注.为了实现同时多层的选择性激发,现有的多层成像序列大多使用组合射频(RF)脉冲,该脉冲可包含多个独立的幅值相同相位不同的简单脉冲,由于其采用简单的线性叠加方法,该类脉冲射频功率随脉冲数量呈现平方增长,因而应用受限.针对这一问题,基于自旋动力学和优化控制原理,本文提出了一种针对同时多层MRI的选择性射频脉冲的数值优化方法,该方法充分运用射频脉冲的调控机制,获得优化脉冲,并配合层选梯度,可实现任意层厚、层间距、层数的同时高效选择性激发.最后,通过数字模体的同时多层模拟成像实验验证了优化脉冲的有效性.

A radio-frequency source using direct digital synthesis and field programmable gate array for nuclear magnetic resonance

[J].

A complete digital radio-frequency source for nuclear magnetic resonance spectroscopy

[J].

B1+ shimming with SAR reduction in high-field MRI

[J].

A new approach to design a frequency synthesizer using direct digital synthesis technique

[C]//

All-digital FPGA-based RF pulsed transmitter with hardware complexity reduction techniques

[C]//

Point-of-care brain MRI: preliminary results from a single-center retrospective study

[J].

A low-cost and shielding-free ultra-low-field brain MRI scanner

[J].

DOI:10.1038/s41467-021-27317-1

PMID:34907181

Magnetic resonance imaging is a key diagnostic tool in modern healthcare, yet it can be cost-prohibitive given the high installation, maintenance and operation costs of the machinery. There are approximately seven scanners per million inhabitants and over 90% are concentrated in high-income countries. We describe an ultra-low-field brain MRI scanner that operates using a standard AC power outlet and is low cost to build. Using a permanent 0.055 Tesla Samarium-cobalt magnet and deep learning for cancellation of electromagnetic interference, it requires neither magnetic nor radiofrequency shielding cages. The scanner is compact, mobile, and acoustically quiet during scanning. We implement four standard clinical neuroimaging protocols (T1- and T2-weighted, fluid-attenuated inversion recovery like, and diffusion-weighted imaging) on this system, and demonstrate preliminary feasibility in diagnosing brain tumor and stroke. Such technology has the potential to meet clinical needs at point of care or in low and middle income countries.© 2021. The Author(s).

Portable, bedside, low-field magnetic resonance imaging for evaluation of intracerebral hemorrhage

[J].

DOI:10.1038/s41467-021-25441-6

PMID:34433813

Radiological examination of the brain is a critical determinant of stroke care pathways. Accessible neuroimaging is essential to detect the presence of intracerebral hemorrhage (ICH). Conventional magnetic resonance imaging (MRI) operates at high magnetic field strength (1.5-3 T), which requires an access-controlled environment, rendering MRI often inaccessible. We demonstrate the use of a low-field MRI (0.064 T) for ICH evaluation. Patients were imaged using conventional neuroimaging (non-contrast computerized tomography (CT) or 1.5/3 T MRI) and portable MRI (pMRI) at Yale New Haven Hospital from July 2018 to November 2020. Two board-certified neuroradiologists evaluated a total of 144 pMRI examinations (56 ICH, 48 acute ischemic stroke, 40 healthy controls) and one ICH imaging core lab researcher reviewed the cases of disagreement. Raters correctly detected ICH in 45 of 56 cases (80.4% sensitivity, 95%CI: [0.68-0.90]). Blood-negative cases were correctly identified in 85 of 88 cases (96.6% specificity, 95%CI: [0.90-0.99]). Manually segmented hematoma volumes and ABC/2 estimated volumes on pMRI correlate with conventional imaging volumes (ICC = 0.955, p = 1.69e-30 and ICC = 0.875, p = 1.66e-8, respectively). Hematoma volumes measured on pMRI correlate with NIH stroke scale (NIHSS) and clinical outcome (mRS) at discharge for manual and ABC/2 volumes. Low-field pMRI may be useful in bringing advanced MRI technology to resource-limited settings.© 2021. The Author(s).

Brain imaging with portable low-field MRI

[J].

DOI:10.1038/s44222-023-00086-w

PMID:37705717

[本文引用: 1]

The advent of portable, low-field MRI (LF-MRI) heralds new opportunities in neuroimaging. Low power requirements and transportability have enabled scanning outside the controlled environment of a conventional MRI suite, enhancing access to neuroimaging for indications that are not well suited to existing technologies. Maximizing the information extracted from the reduced signal-to-noise ratio of LF-MRI is crucial to developing clinically useful diagnostic images. Progress in electromagnetic noise cancellation and machine learning reconstruction algorithms from sparse -space data as well as new approaches to image enhancement have now enabled these advancements. Coupling technological innovation with bedside imaging creates new prospects in visualizing the healthy brain and detecting acute and chronic pathological changes. Ongoing development of hardware, improvements in pulse sequences and image reconstruction, and validation of clinical utility will continue to accelerate this field. As further innovation occurs, portable LF-MRI will facilitate the democratization of MRI and create new applications not previously feasible with conventional systems.

Compact multi-channel radio frequency pulse-sequence generator with fast-switching capability for cold-atom interferometers

[J].

Design, implementation, evaluation and application of a 32-channel radio frequency signal generator for thermal magnetic resonance based anti-cancer treatment

[J].

A multi-source RF transmitter for high-field MRI

[J].

一种用于高场MRI的多源射频发射机

[J].

DOI:10.11938/cjmr20162533

[本文引用: 1]

介绍了高场磁共振成像(MRI)多源发射技术的原理,提出了一种用于高场MRI系统的多源射频信号发射机.它能并行输出多路频率、相位、幅度,可快速独立调节的射频脉冲信号.该射频发射机的实现基于单片现场可编程门阵列(FPGA)和多通道数模转换器(DAC)芯片,FPGA读取预存于双端口随机存取存储器(RAM)中的射频信号参数,并利用读取的参数分别实现每路信号的直接数字频率合成(DDS)和信号调制等核心功能,获得多路数字射频信号;FPGA输出的数字信号经过高性能DAC转化为模拟信号,即所需要的射频信号.该射频发射机在设计中大量采用软件无线电技术,即利用Xilinx提供的IP核实现DDS和信号调制等主要功能,具有集成度高、体积小、灵活度高的优点,同时,该设计可以大大缩短开发时间,有效降低实现的难度和成本,为高场MRI谱仪的多源射频发射机的设计研制提供了一种低成本、高效、高性价比的方案.